| Siguiente: 6. Uso del driver Superior: Hospedaje Linux de multicomputadores Anterior: 4. Perfil y evolución |

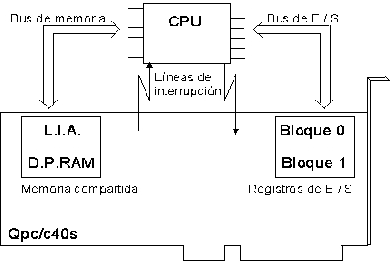

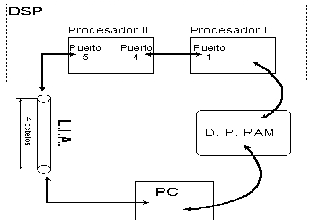

La Fig. 8 muestra un esquema general de la interfaz PC huésped-QPC/C40S.

La interfaz entre el PC y la tarjeta consiste en tres recursos de comunicación:

0A 0000h, 0B 0000h, 0C 0000h y 0D 0000h.

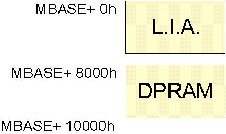

En el manual de la QPC este valor es denominado Memory Base o MBASE. La dirección elegida se escribe en el registro Base Address Register del bloque 0 (junto con la dirección del bloque 1 de registros). El mapeo se raliza automáticamente por hardware. La organización interna de esta memoria es la siguiente:

Hay que tener en cuenta que un proceso de usuario maneja direcciones virtuales de su espacio de direccionamiento, y no direcciones físicas del PC. Por eso para acceder a esta zona de memoria física hay que hacerlo desde un módulo añadido al sistema operativo o mapear esa memoria en un buffer de usuario con la llamada mmap. En este caso hemos hecho lo primero, el driver ofrece operaciones de lectura y escritura (read y write) sobre la memoria compartida, para que los procesos de usuario puedan utilizarla.

El C44 dispone de 4 canales de comunicación que lo conectan con el exterior (el procesador C40 tiene 6) y hacen del mismo un procesador idóneo para el proceso paralelo. Estos puertos interconectan dos procesadores C44 o bien comunican al procesador con un puerto externo del módulo TIM o de la tarjeta. Están mapeados en la memoria del C40, pudiéndose leer o escribir libremente ya que están controlados por una unidad de arbitraje que regula la comunicación bidireccional.

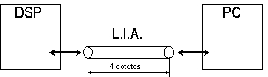

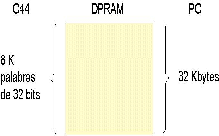

La interfaz LIA ocupa los primeros 32 KB de la memoria compartida (Fig. 9). Puede verse como un medio para intercambiar datos entre el PC y un C44, donde la comunicación es bidireccional y la unidad de intercambio son 4 octetos (Fig. 10).

Desde el punto de vista del procesador DSP, LIA es un puerto más de comunicación, sin ninguna diferencia especial. Del lado del PC, la interfaz LIA es el resultado de mapear un puerto de un C44 en 4 Bytes de la memoria compartida del PC. Esta interfaz está indicada para el intercambio de flujos de datos.

Los puertos de comunicación de los C44 son rutados por hardware. Cada uno se conecta a otro procesador o dispositivo, dependiendo de la decisión de los fabricantes del módulo TIM y de la tarjeta. En nuestra QPC-C40S el puerto número 2 del módulo A (A2) es rutado hacia el módulo B, LIA está conectada al puerto 5 del módulo A, y dicho puerto está conectado al puerto 5 del procesador II. Esto significa que LIA comunica al PC con el puerto 5 del procesador II del módulo A.

Vamos a ocuparnos ahora de la interfaz LIA en el lado del PC. Aunque LIA ocupa 32 KB de la memoria compartida, sólo se utilizan los cuatro primeros Bytes. LIA se configura internamente como sigue:

| M_BASE | 1º octeto / 2º octeto |

| M_BASE + 2 | 3º octeto / 4º octeto |

| (Sin uso) |

Esos cuatro octetos forman la palabra de 32 bits a leer o escribir en cada momento. En el manual de la tarjeta no se informa de cómo se escriben y se leen los datos, ni el sitio concreto donde hay que hacerlo (dentro de la memoria destinada a LIA). El registro LIA Status / Interrupt del primer bloque contiene dos bits que informan de cuándo LIA está lista para ser leída, y cuándo está lista para ser escrita. Lo que significa que antes de usar LIA hay que leer esos bits del registro LIA Status/Interrupt. Aparentemente se puede leer y escribir en cualquier punto del rango dedicado a LIA, y el resultado es el mismo. Nuestro driver lee y escribe en los 4 primeros Bytes (como muestra la tabla anterior).

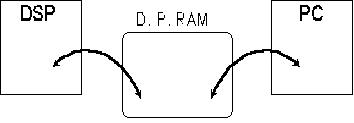

El segundo bloque de 32 KB de memoria compartida (Fig. 9) los ocupa DPRAM, un auténtico buffer compartido entre un C44 y el PC huésped, según muestra la Fig. 11. No hay ninguna restricción sobre cómo debe usarse esta memoria; todo depende del acuerdo entre los procesadores.

Como se puede apreciar esta interfaz está más indicada para intercambiar estructuras de datos, que pueden haber sido construidas en la propia memoria compartida.

Sólo el módulo TIM A tiene acceso a DPRAM, y dentro de este módulo la memoria compartida sólo está mapeada en la memoria del procesador I. Así, la interfaz DPRAM puede concretarse con la Fig.12.

Como se trata de una memoria compartida entre el PC y un C44, la gestión de este recurso queda en manos de los programadores. Los fabricantes de la tarjeta sugieren que se implemente un protocolo de semáforo, para evitar acceso simultáneo a los datos. Hay que tener en cuenta que el C44 accede a esta memoria en unidades de 32 bits, mientras que el PC accede en unidades de 8 bits.

En el procesador I del módulo TIM A, la memoria compartida comienza en la posición A0100000h y se extiende sobre 8 KB, teniendo en cuenta que en un C44 un Byte son 32 bits. En el PC la memoria compartida comienza 32KB (8000h) por debajo de MBASE, que es lo que ocupa LIA. En la Fig. 13, la dirección de comienzo es D8000h, porque se supone que MBASE ha sido configurado al valor 0D0000h. DPRAM se extiende en el PC 32 KB a partir de esa dirección de comienzo.