#### Universal Host Controller Interface (UHCI) Design Guide

**REVISION 1.1**

March 1996

The information in this document is under review and is subject to change.

### THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

**IN**

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to implementation of information in this specification. Intel does not warrant or represent that such implementation(s) will not infringe such rights.

A license is hereby granted to copy this document for internal use only. No other license, express or implied, by estoppel or otherwise, to any other intellectual property rights is granted herein. If you wish to implement the Universal Host Controller Interface, please refer to the licensing terms on the following page.

\*Other brands and names are the property of their respective owners.

Copyright © Intel Corporation 1996

#### **Universal Host Controller Agreement**

This is a royalty-free, reciprocal license for Adopters of the USB Specification who wish to implement the Universal Host Controller Interface designed by Intel, and described in the Universal Host Controller Interface (UHCI) Design Guide, in their USB-compliant products. By implementing this specification, you ("User") are agreeing to be bound by the terms of this agreement. If you do not agree to them, then you have no license to use the specification, and you should destroy these materials or return them to Intel.

**Eligible Licensees:** The licenses granted in this Agreement shall only extend to a party who has executed and is bound by the agreement executed by Intel and other parties entitled "USB Reciprocal Covenant" relating to the USB Specification.

Agreement: Effective as of User's acceptance of this Agreement, and subject to its terms and conditions, Intel Corporation ("Intel") and User agree as follows:

License: Intel and User each grant to the other and its parents and subsidiaries, under any claim of a patent or patent application otherwise infringed, a non-exclusive, royalty-free, non-transferable, world-wide license, without rights to sublicense, to make or have made such party's products which implement the Interface solely in connection with implementing the USB Specification, and to use, sell, offer to sell, and import such products, where infringement of such claims would not have occurred but for the implementation and incorporation of the Interface in such products, and there is no feasible alternative to such infringement.

"Interface" means interface specification described in the document entitled "Universal Host Controller Interface (UHCI) Design Guide" published by Intel, and any circuitry described therein.

"USB Specification" means a revision of the "Universal Serial Bus Specification," numbered 1.0 or greater, published and made available for industry licensing by Intel and the other USB promoters.

**No Other Licenses.** Except for the rights expressly provided by this Agreement, neither party grants or receives, by implication, or estoppel, or otherwise, any rights under any patents or other intellectual property rights. Licenses to the USB Specification are to be granted by a separate document.

**LIMITATION OF LIABILITY:** The Interface is provided "AS IS" without warranty of any kind. INTEL OFFERS NO OTHER WARRANTY EITHER EXPRESS OR IMPLIED INCLUDING THOSE OF MERCHANTABILITY, NONINFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY OR FITNESS FOR A PARTICULAR PURPOSE. NEITHER INTEL NOR ITS SUPPLIERS SHALL BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER LOSS) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INTERFACE, EVEN IF INTEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF LIABILITY FOR CONSEQUENTIAL OR INCIDENTAL DAMAGES, THE ABOVE LIMITATION MAY NOT APPLY TO YOU.

**TERMINATION OF THIS LICENSE**: Intel may terminate this license at any time if you are in breach of any of its terms and conditions. Upon termination, you will immediately destroy the Interface or return all copies of the Interface to Intel along with any copies you have made.

<u>U.S. GOVERNMENT RESTRICTED RIGHTS</u>: The Interface is provided with "RESTRICTED RIGHTS." Use, duplication or disclosure by the Government is subject to restrictions set forth in FAR52.227-14 and DFAR252.227-7013 <u>et seq.</u> or its successor. Use of the Interface by the Government constitutes acknowledgment of Intel's rights in them .

<u>APPLICABLE LAWS</u>: Any claim arising under or relating to this Agreement shall be governed by the laws of Delaware. You may not export the Interface in violation of applicable export laws.

int<sub>el</sub>.

#### **Table Of Contents**

| 1. OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1.1 DATA TRANSFER TYPES         1.1.1 FRAME TIME FOR DATA TRANSFERS         1.2 UHCI DATA STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                                        |

| 1.2.1 FRAME LIST<br>1.2.2 TRANSFER DESCRIPTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                        |

| 1.2.3 QUEUE HEADS<br>1.3 SCHEDULING<br>1.3.1 HARDWARE CONTROL FOR FULL SPEED TRANSFER BANDWIDTH RECLAMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                        |

| 1.4 ROOT HUB/PORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

| 2.1 USB I/O REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                       |

| 2.1.2 USBSTS—USB STATUS REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                                       |

| 2.1.4 FRNUM—FRAME NUMBER REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                       |

| 2.1.6 START OF FRAME (SOF) MODIFY REGISTER<br>2.1.7 PORTSC—PORT STATUS AND CONTROL REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                       |

| 2.2.1 CLASSC—CLASS CODE REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                       |

| 2.2.2 USBBASE—IO SPACE BASE ADDRESS REGISTER<br>2.2.3 SBRN—SERIAL BUS RELEASE NUMBER REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                                       |

| 3. DATA STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                                       |

| 3. DATA STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                                       |

| 3.1 FRAME LIST POINTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                       |

| 3.1 FRAME LIST POINTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20<br>20                                                                                                 |

| 3.1 FRAME LIST POINTER.<br>3.1.1 FRAME LIST POINTER (DWORD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20<br>20<br>20                                                                                           |

| <ul> <li>3.1 FRAME LIST POINTER</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>20<br>20<br>21                                                                                     |

| <ul> <li>3.1 FRAME LIST POINTER</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>20<br>20<br>21<br>22<br>24                                                                         |

| <ul> <li>3.1 FRAME LIST POINTER</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>20<br>21<br>22<br>24<br>25                                                                         |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20<br>20<br>21<br>22<br>24<br>25<br>25                                                                   |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25                                                             |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H).</li> </ul>                                                                                                                                                                                                                                                                                                                                                           | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>25                                                       |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26                                                       |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H)</li> </ul>                                                                                                                                                                                                                                                                                                | 20<br>20<br>21<br>22<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>26                                     |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H)</li> <li>3.4 SCRIPT AND DATA TRANSFER PRIMITIVES</li> <li>3.4.1 EXECUTING THE SCHEDULE</li> </ul>                                                                                                                                                                                                         | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>26<br>21                         |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H).</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H)</li> <li>3.4 SCRIPT AND DATA TRANSFER PRIMITIVES.</li> <li>3.4.1 EXECUTING THE SCHEDULE</li> <li>3.4.2 TRANSFER QUEUING.</li> </ul>                                                                                                                                                                      | 20<br>20<br>21<br>22<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>31<br><b>35</b>                        |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD).</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H).</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H).</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH).</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORD 3: 0C-0FH).</li> <li>3.3 QUEUE HEAD (QH).</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H)</li></ul>                                                                                                                                                                                                                                                                                                                                                     | 20<br>20<br>21<br>22<br>25<br>25<br>26<br>26<br>26<br>31<br><b>35</b><br>35                              |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH)</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4])</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD (QH)</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 0: 00-03H)</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H)</li> <li>3.4 SCRIPT AND DATA TRANSFER PRIMITIVES.</li> <li>3.4.1 EXECUTING THE SCHEDULE</li> <li>3.4.2 TRANSFER QUEUING</li> <li>4. INTERRUPTS</li> <li>4.1 TRANSACTION BASED</li> <li>4.1.1 CRC ERROR / TIME-OUT</li> <li>4.1.2 INTERRUPT ON COMPLETION (IOC)</li> </ul> | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>31<br><b>35</b><br>35<br>35            |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H).</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H).</li> <li>3.4 SCRIPT AND DATA TRANSFER PRIMITIVES.</li> <li>3.4.1 EXECUTING THE SCHEDULE</li> <li>3.4.2 TRANSFER QUEUING.</li> <li>4. INTERRUPTS.</li> <li>4.1 TRANSACTION BASED.</li> <li>4.1.1 CRC ERROR / TIME-OUT</li> <li>4.1.3 SHORT PACKET DETECT (SPD).</li> </ul>                               | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>31<br>35<br>35<br>35<br>35             |

| <ul> <li>3.1 FRAME LIST POINTER</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>31<br>35<br>35<br>35<br>36<br>36       |

| <ul> <li>3.1 FRAME LIST POINTER.</li> <li>3.1.1 FRAME LIST POINTER (DWORD).</li> <li>3.2 TRANSFER DESCRIPTOR (TD)</li> <li>3.2.1 TD LINK POINTER (DWORD 0: 00-03H)</li> <li>3.2.2 TD CONTROL AND STATUS (DWORD 1: 04-07H)</li> <li>3.2.3 TD TOKEN (DWORD 2: 08-0BH).</li> <li>3.2.4 TD BUFFER POINTER (DWORD 3: 0C-0FH)</li> <li>3.2.5 RESERVED FOR SOFTWARE (DWORDS [7:4]).</li> <li>3.3 QUEUE HEAD (QH)</li> <li>3.3.1 QUEUE HEAD LINK POINTER (DWORD 0: 00-03H).</li> <li>3.3.2 QUEUE ELEMENT LINK POINTER (DWORD 1: 04-07H).</li> <li>3.4 SCRIPT AND DATA TRANSFER PRIMITIVES.</li> <li>3.4.1 EXECUTING THE SCHEDULE</li> <li>3.4.2 TRANSFER QUEUING.</li> <li>4. INTERRUPTS.</li> <li>4.1 TRANSACTION BASED.</li> <li>4.1.1 CRC ERROR / TIME-OUT</li> <li>4.1.3 SHORT PACKET DETECT (SPD).</li> </ul>                               | 20<br>20<br>21<br>22<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>31<br>35<br>35<br>35<br>36<br>36<br>36 |

#### Universal Host Controller Interface (UHCI), Revision 1.1

| 4.2 NON-TRANSACTION BASED                                             |    |

|-----------------------------------------------------------------------|----|

| 4.2.1 RESUME RECEIVED                                                 | 37 |

| 4.2.2 HOST CONTROLLER PROCESS ERROR                                   | 37 |

| 4.2.3 HOST SYSTEM ERROR                                               | 37 |

| 5. KEYBOARD AND MOUSE LEGACY SUPPORT                                  |    |

| 5.1 OPERATION                                                         |    |

| 5.1.1 COMMANDS GOING TO THE KBC, KEYBOARD, OR MOUSE                   |    |

| 5.1.2 KEYSTROKE OR MOUSE DATA RECEIVED                                |    |

| 5.2 REGISTER INTERFACE                                                |    |

| 5.2.1 LEGSUP—LEGACY SUPPORT REGISTER (PCI CONFIGURATION - FUNCTION 2) |    |

| 5.2.2 KBC ACCESS LOGIC                                                |    |

| 5.3 OTHER CONSIDERATIONS                                              | 41 |

#### **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                              |

|------------------|---------|----------------------------------------------------------------------------------------------------------|

| November, 1995   | 1.0     | Original Version                                                                                         |

| March 21, 1996   | 1.1     | Additional USB 0.99 to 1.0 specification changes, clarifications, and Legacy Keyboard and Mouse support. |

#### **Universal Host Controller Interface (UHCI)**

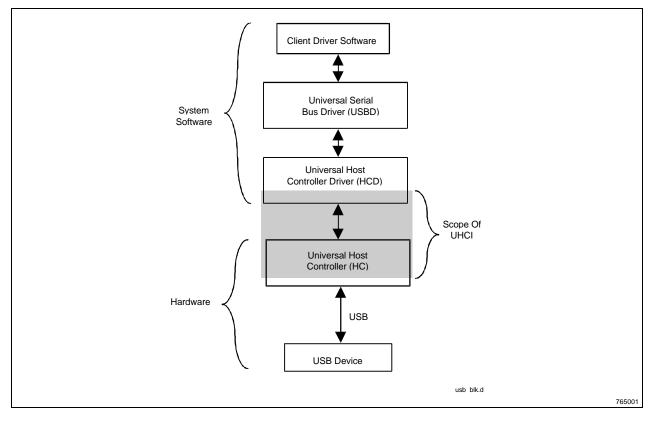

This document describes a Universal Host Controller Interface (UHCI) for a device that implements a Universal Serial Bus (USB) Host Controller. The document is intended for hardware vendors. The UHCI description covers the hardware/software interface between the Host Controller Software Driver and the Host Controller hardware (shaded area in Figure 1). It describes the register-level hardware interface to the USB Host Controller. Hardware developers may take advantage of the standard software drivers written to be compatible with this Universal Host Controller Interface by conforming to the register level interface and memory data structures described in this document.

The UHCI consists of two parts—Host Controller Driver (HCD) and Host Controller (HC). The HCD software is responsible for scheduling the traffic on USB by posting and maintaining transactions in system memory. HCD is part of the system software and is typically provided by the operating system vendor. For example, Microsoft Corporation will fully support UHCI.

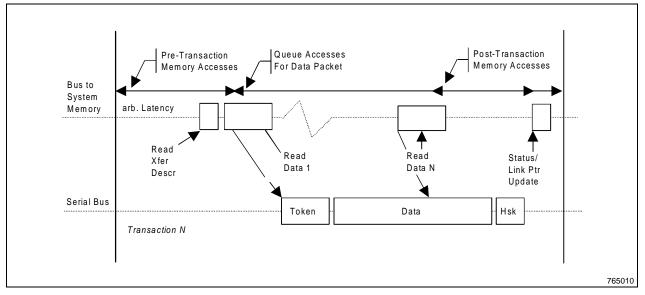

The Host Controller moves data between system memory and devices on the USB by processing these data structures and generating the transaction on USB. Note that the high transfer rates on USB means that the Host Controller should use a high bandwidth interface to system memory. For the implementation example in this document, the Host Controller is a PCI device. PCI Bus master capability in the Host Controller permits high performance data transfers to system memory.

Some of the key features of UHCI include:

- Ease Of Use. The reduced hardware complexity makes the Host Controller easy to implement. In addition, standard UHCI software drivers (HCD) will be supported by companies like Microsoft Corporation. Other operating system vendors can make use of the portability of the HCD software. Note that the run-time portion of the HCD software is operating system independent. The initialization code is easily tailored for a particular operating system.

- Minimize Cost. An optimal partition between software and hardware operations was selected to minimize Host Controller gate count, maximize performance, and maintain flexibility.

- Flexibility. The UHCI Host Controller can be implemented in a wide range of products from a stand-alone device to integration into a PCI chipset.

- Reduced Hardware Complexity. The Host Controller can be implemented with about 10,000 gates. The low gate count and few number of pins needed makes this function easily integrated into a chipset. The UHCI software/hardware interface was designed to minimize Host Controller hardware complexity.

- Data structures are manipulated by the Host Controller in a very simple fashion. All pointers are set by software and the only operation by the hardware is a copy of the link pointers. No numerical operations are required on data structure pointers.

- The basic data structure (transfer descriptor) for both isochronous and queued transfers use the same form (fields in the structure determine transfer type behaviors). This simplifies decode logic.

- The Host Controller transfers the appropriate data over USB by executing a schedule list of transactions set up in system memory by the HCD software. In UHCI, the Host Controller execution of this schedule is inherently tied directly to the real-time nature of isochronous transfers. The frame counter in the Host Controller that is needed to provide a frame count number for the Start Of Frame (SOF) packet is also used to index into the schedule list. No address calculations are necessary. The Host Controller simply walks the schedule list one entry at a time as it generates the next 1 ms frame.

- The UHCI register set can be implemented with eight hardware registers, including two root hub port registers. To prevent conflicts with other I/O devices, the USB I/O register set can be re-located in the I/O address space by programming one of the Host Controller's PCI configuration registers.

- Increased System Performance. UHCI maximizes the use of the USB bus and minimizes the impact on other system buses.

- UHCI minimizes end of frame idle time on USB. Potentially idle time in a 1-ms USB frame can be reclaimed to within a 32- or 64-byte packet.

- Data structures and their manipulation by the Host Controller were designed to minimize bus traffic to system memory. For example, during isochronous transfers, the Host Controller only needs to fetch one data structure (transfer descriptor) from system memory to generate a transaction.

- Legacy Keyboard and Mouse Support. While not required by UHCI, Section 5 documents a method to provide support for legacy software which directly accesses an 8042 device-based keyboard and mouse controller.

Figure 1. Universal Serial Bus System Block Diagram

#### 1. OVERVIEW

A USB Host System is composed of a number of hardware and software layers. Figure 1 shows a conceptual representation of these layers.

- USB Driver (USBD). The USBD system software that supports USB in a particular operating system.

- Client driver software. This software executes on the host PC corresponding to a particular USB device. Client software is typically part of the operating system or provided with the USB device.

- Host Controller Driver (HCD). HCD provides the software layer between the Host Controller hardware and the USBD. The UHCI's HCD interprets requests from the USBD and builds Frame List, Transfer Descriptor, Queue Head, and data buffer data structures for the Host Controller. The data structures are built in system memory and contain all necessary information to provide end-to-end communication between client software in the host and devices on the USB.

- Host Controller (HC). The Host Controller is managed by the HCD software layer. The UHCI's Host Controller executes the schedule lists generated by HCD and reports the status of transactions on the USB to HCD.

Command execution includes generating serial bus token and/or data packets based on the command and initiating transmission on USB. For commands that require the Host Controller to receive data from the USB device, the Host Controller receives the data and then transfers it to the system memory pointed to by the command. The UHCI's HCD provides sufficient commands and data to keep ahead of the Host Controller execution and analyzes the results as the commands are completed.

• USB Device. This is a hardware device that performs a useful end-user function. Interactions with USB devices flow from the applications through the software and hardware layers to the USB devices.

#### 1.1 Data Transfer Types

USB transfers data associated with client software on the host to an endpoint on a USB device. A particular device may have multiple endpoints. USB defines four transfer types:

- **Isochronous.** The Isochronous type is characterized by a constant, fixed rate transfer between the USB device and the host. This service is needed for devices that continuously consume or produce data at a fixed rate. Some examples of this class of device would be audio CODECs (microphones or speaker systems) and telephony devices. Isochronous service does not guarantee data delivery. Failed transactions are not retried. The Isochronous data structure elements are always retired after execution, regardless of the outcome of the transaction. See Data Structure section for a definition of Transfer Descriptors (Active Bit).

- Interrupt. Small, spontaneous data transfers from a device. The Interrupt transfer type supports devices that require a predictable service interval but do not necessarily produce a predictable flow of data. Interrupt transfers are input only and typically used for devices such as keyboards and pointing devices that may not produce data for long periods of time but require quick response when they do have data to send.

- **Control.** Transfers that convey device control, status, and configuration information. The Control transfer type is used to provide a control channel from the Host to USB devices. Control transfers always consist of a setup phase and zero or more data phases followed by a status phase. It is critical that control transfers to a given endpoint are handled in a FIFO manner. If Control transfers to the same endpoint are interleaved, unpredictable behavior could result.

- Bulk. The purpose of Bulk traffic is to provide a guaranteed transmission of data between client and host under relaxed latency requirements. This transfer type is typically used by devices that need to move large amounts of data but are able to tolerate relatively large service latencies (e.g., printers).

To provide a guaranteed delivery mechanism, Interrupt, Control, and Bulk Transfer Descriptors are retried if they do not complete successfully. The number of times that a particular Transfer Descriptor is retried is bounded by the cumulative error counter contained in the Transfer Descriptor. If the permitted error count is exhausted, the Host Controller deactivates the Transfer Descriptor by clearing its ACTIVE bit. Software must provide any error recovery mechanism required to deal with the problem.

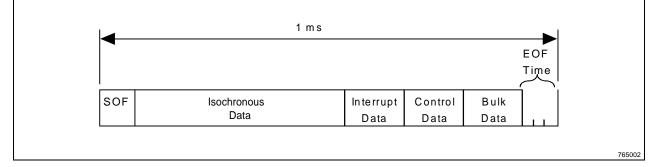

On the USB, 1-ms frame times are used to transfer data. The Host Controller begins each frame by generating a Start Of Frame (SOF). In UHCI, if there is isochronous data to be transferred, the Host Controller Driver schedules this data first. The Host Controller Driver ensures that there is enough time to complete all scheduled isochronous and interrupt transfers with some time remaining for control and bulk transfers (see Scheduling Section).

Figure 2. Transfer Type Schedule Order

### intel

#### Universal Host Controller Interface (UHCI), Revision 1.1

#### 1.1.1 FRAME TIME FOR DATA TRANSFERS

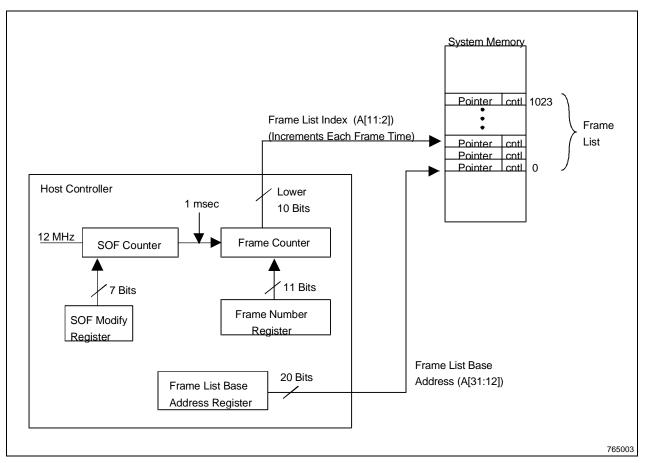

The Host Controller supports real-time data delivery by generating a Start Of Frame (SOF) packet every 1 ms. The SOF packet is generated when the SOF Counter in the Host Controller (Figure 3) expires. The Host Controller initializes the SOF Counter for a 1-ms frame time. Minor adjustments can be made to this value (and thus, the frame time period) by programming the SOF Modify Register. This feature permits minor changes to be made to the frame time period, if necessary, to maintain real-time synchronization throughout a USB system.

The Host Controller includes a frame number in each SOF packet. This frame number uniquely identifies the frame period in real time. The End of Frame (EOF) condition occurs at the end of the 1-ms time interval at which time the Host Controller begins the next frame time by generating another SOF packet with its corresponding frame number. Inside a frame period, data is transferred as packets of information. The frame time period is strictly enforced by the Host Controller and data packets in the current frame are not allowed to extend beyond the EOF (see Chapter 11 in the Universal Serial Bus Specification).

The Host Controller maintains real-time frame-to-data transfer synchronization by tying the frame number to the execution of a particular entry in the Frame List. The Host Controller's Frame Counter generates the frame number (11-bit value) and includes it in each SOF packet. The counter is programmable via the Frame Number Register and increments every frame period.

The Host Controller uses the lower 10 bits of the frame number as an index into a 1024 entry Frame List that is stored in system memory. Thus, since the frame count drives the Frame List entry selection, the Host Controller processes each Frame List entry in a prescribed frame period. The Host Controller increments to the next Frame List entry for each new frame. This ensures that isochronous transfers are executed in a particular frame.

Figure 3. Frame Number Ties Frame List to Real Time

#### 1.2 UHCI Data Structures

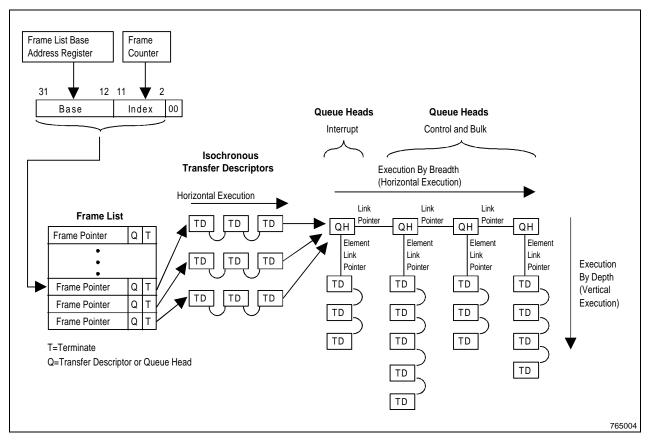

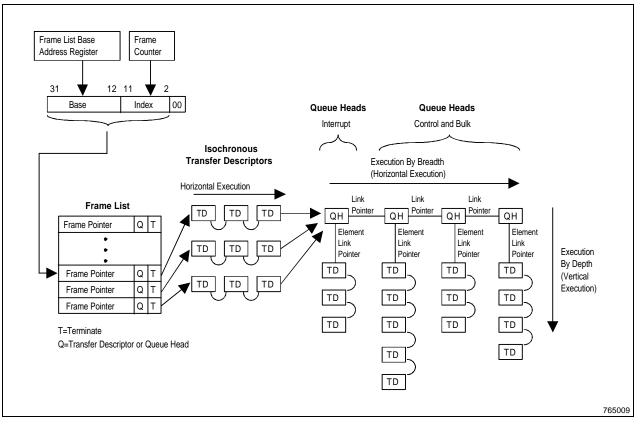

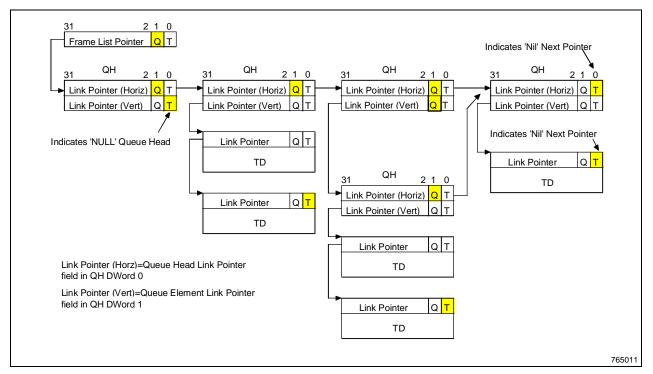

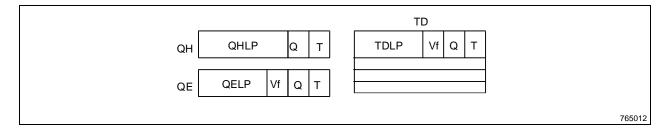

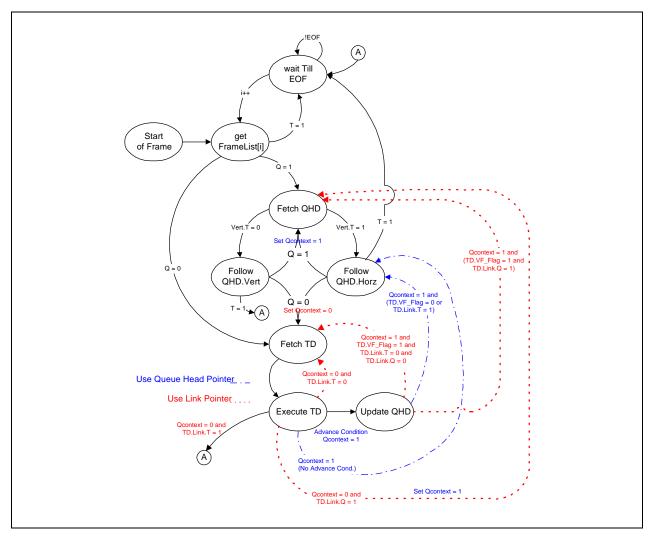

The UHCI data structures include a Frame List, Isochronous Transfer Descriptors, Queue Heads, and queued Transfer Descriptors. These data structures are used by HCD software to construct a "schedule" in host memory for the Host Controller to execute (Figure 4). The Host Controller is programmed with the starting address of the Frame List, then released to "execute" the schedule, without any overt synchronization with HCD. Transfer descriptors point to data buffers and include information about the addressing, data, and general behavior characteristics of the transaction.

Flow through the schedule is based on link pointers in the Frame List, Transfer Descriptors, and Queue Heads. Link Pointers are the fundamental component used to connect all the scheduled data "objects" together. The Host Controller uses the link pointer to determine where to find the next transfer descriptor to execute. Addresses in the link pointer fields must be a physical address and not a virtual address.

At the start of a frame, the Host Controller repeatedly follows link pointers, beginning at the current Frame List index, pausing its traversal to perform transactions described in Transfer Descriptors, and stopping when the frame expires (or a terminate bit is set on a horizontal flow execution).

#### 1.2.1 FRAME LIST

The Frame List is an array of up to 1024 entries that represent a window in time. Each entry corresponds to a particular frame (1 ms). An entry serves as a reference to the transactions the Host Controller should conduct during that frame. Each entry contains a pointer to other data structures (Transfer Descriptors or Queue Heads) and control bits. The Host Controller does not update fields in the Frame List. The fields in the Frame List entries are managed by HCD software.

The Host Controller accesses the Frame List using the contents of the Frame List Base Address Register and the Frame Counter (Figure 3). The Frame List Base Address Register provides the base location of the Frame List Table in system memory and the Frame Counter provides the index into the list. The 4-Kbyte Frame List Table is aligned on a 4-Kbyte boundary.

The Host Controller does not execute beyond the 1 ms allocated to the current frame. HCD insures that any manipulation of entries be accomplished in a way that does not cause a coherency problem if the Host Controller needs to access the same entry.

#### **1.2.2 TRANSFER DESCRIPTORS**

Transfer Descriptors (TDs) contain a pointer to a data buffer and contain control and status fields for the data and its transmission or reception. Note that a TD could optionally have no data buffer associated with it (i.e., NULL data). There are TDs for isochronous transfers and queued transfers (interrupt TDs, control TDs, and bulk TDs). All TDs have the same structure. During execution, the Host Controller may update fields in the TD, as appropriate. It must maintain the TD in a consistent state (i.e., not allow accesses to partially modified TD).

For isochronous operations, the UHCI HCD software builds separate TDs for each transfer and links them into the schedule in the correct frame as requested by USBD. All temporal ordering is the responsibility of software. The Host Controller fetches the TD and generates the proper transaction on USB. The execution flow is always horizontal as shown in Figure 4. For isochronous transfers, TDs are linked to a specific point in real time. TDs that do not complete successfully on time are not retried. In the example in Figure 4, the TD list is horizontally executed until the end of the TD list is reached. The last TD in the list points to a Queue Head for processing of queued Transfer Descriptors.

For non-isochronous operations see Section 1.2.3—Queue Heads.

# intel

Figure 4. Example Schedule

#### 1.2.3 QUEUE HEADS

Queue Heads (QH) are data structures that organize non-isochronous transfer descriptors into queues. A QH and associated TD list form a "*Q Context*". Interrupt, Control, and Bulk, data transfer types can be placed in queues. The UHCI first services Interrupt queues followed by control queues and if there is time remaining, bulk queues. During execution, the Host Controller updates fields in the TDs and QHs, as appropriate.

Queues can be accessed directly from a Frame List entry or from the last TD in an isochronous TD list. Queues can also be accessed from a prior Queue Context. QHs contain two link pointers—a vertical pointer that selects the next TD in the Q Context to be processed and a horizontal pointer that provides a link to the next QH or TD to be processed. Note that the vertical pointer could also point to another QH. See the "Transfer Queuing" section for additional information on Queues. Queued transfers that do not complete successfully can be retried.

When queues are being processed, execution flow can be from one TD to the next within a Q Context (execution by depth) or from one QH to the next QH (execution by breadth) where only one TD in each Q Context is executed at a time. A field in the executing TD ( Vf field) determines whether the execution is by depth or breadth.

For execution by depth, the execution flow traverses vertically through the TDs of the same Q Context until the end is reached or TD execution is blocked; in which case, the execution flow moves to the next QH in the link. For execution by breadth, one TD is executed in a Q Context and then the flow is to the next QH where the first TD in that Q Context is executed, and so on. See Section 3.4 for a more complete description.

#### 1.3 Scheduling

The HCD software sets up and manages the data structures to ensure that Isochronous traffic has the highest priority in the Host Controller. The HCD scheduling allows up to 90% of the frame bandwidth to be allocated to isochronous and interrupt traffic, and up to 10% of the frame bandwidth for control. Any remaining bandwidth can be reclaimed for control and bulk transfers.

Scheduling with the UHCI is handled by a Frame List (up to 1024 entries). Each entry is a pointer to the first structure to process in a given frame. Because these pointers are a full 32 bits long, a 1024 entry Frame List occupies 4096 bytes of memory (one page).

Control and bulk transfers are scheduled last to allow bandwidth reclamation on a lightly loaded USB. Bandwidth reclamation allows the hardware to continue executing a schedule until time runs out in the frame, cycling through queue entries as frame time allows. Control is scheduled first to prioritize it over bulk transfers. Also, the software does the scheduling to guarantee that at least 10% of the bandwidth is available for control transfers. UHCI only allows for bandwidth reclamation of full speed control and bulk transfers. The software must schedule low speed control transfers such that they are guaranteed to complete within the current frame. Low speed bulk transfers are not allowed by the USB specification. If full speed control or bulk transfers are in the schedule, the last QH points back to the beginning of the full speed control and bulk queues continue to be processed. If bandwidth reclamation is not required, the last QH contains a terminate bit to inform the Host Controller to wait until the beginning of the next frame.

#### 1.3.1 HARDWARE CONTROL FOR FULL SPEED TRANSFER BANDWIDTH RECLAMATION

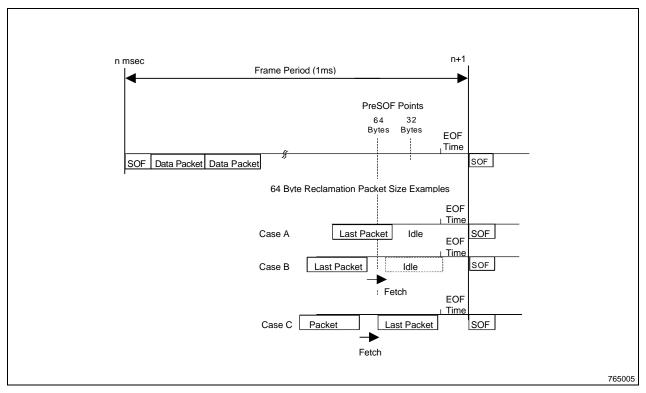

For full speed control and bulk bandwidth reclamation, the Host Controller hardware uses a preSOF time point (Figure 5) to determine if there is enough time to execute the selected size transaction (32- or 64-byte packet size as programmed in the USB Command Register). The preSOF point permits the Host Controller to maximize bandwidth efficiency by reclaiming potential idle time on the bus to within a 32- or 64-byte full speed packet. Note that any packets which may be subjected to bandwidth reclamation must not be any larger in size than the value (32- or 64- byte) programmed into bit 7 of the USB Command register. Note that for any packets larger than the programmed size (32- or 64-byte), the scheduling software must guarantee that bandwidth is available for its completion within the frame.

The preSOF point also prevents a packet that may not fit in the remaining frame period from being initiated. If the preSOF point has already occurred as the Host Controller is transitioning out of the status update phase of the command, the Host Controller does not fetch the next command in this frame (Figure 5, Case A). If the preSOF point is reached during the fetch of the next command's Transfer Descriptor (TD) or during the initial write data fetch (up to 32 bytes), the command is aborted (Figure 5, Case B). No data is written back to memory. If the Host Controller starts the transaction on the bus before preSOF, the command runs to completion, but is the last TD executed in that frame's list (Figure 5, Case C).

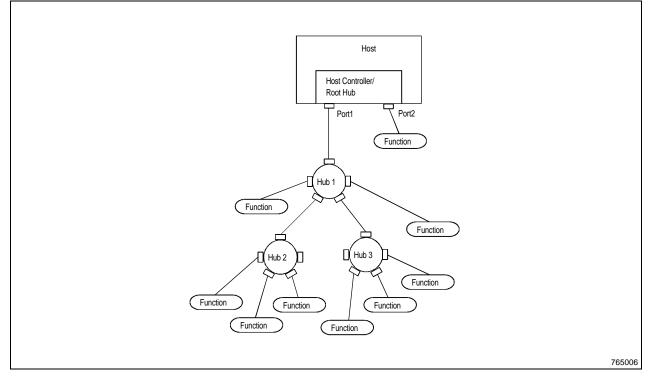

#### 1.4 Root Hub/Ports

The Host Controller is required by the USB Specification to implement the root hub. Hubs provide the electrical interface between USB devices and the host and provide data control for transfers. Hubs can also optionally provide power management capabilities. For the Host Controller implementation described in this design guide, the root hub is integrated into the Host Controller and has two ports (Figure 6). UHCI permits additional ports to be implemented up to the maximum specified by the USB Specification.

The flow of information towards the host is referred to as upstream traffic and the flow of information away is referred to as downstream traffic. For details on hub operations, refer to Chapter 11 of the USB Specification. The UHCI root hub downstream port characteristics and operation conform to the specifications described in chapter 11.

For UHCI implementation described in this design guide, the root hub provides data flow control. Power management control for individual ports is beyond the scope of this UHCI Design Guide.

#### Universal Host Controller Interface (UHCI), Revision 1.1

Figure 6. Hub Topology

#### Universal Host Controller Interface (UHCI), Revision 1.1

Chapter 11 of the USB specification describes software commands used for controlling and obtaining status of hubs and ports. The UHCI's HCD abstracts these commands and uses them to set or read the appropriate bits in the Host Controller registers. These commands are shown in Table 1.

| Command          | Register Name           | Register Bits           | Comment                                                                                                                                                                   |

|------------------|-------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hub Descriptors  | None                    | None                    | Implemented in HCD Software.<br>Does not affect hardware.                                                                                                                 |

| ClearHubFeature  | None                    | None                    | Not part of UHCI Design Guide                                                                                                                                             |

| ClearPortFeature | Port Status and Control | 1, 2, 3, 8, 9, 12       | Register Read or Write.                                                                                                                                                   |

| GetBusState      | Port Status and Control | 4, 5                    | Register Read                                                                                                                                                             |

| GetHubDescriptor | None                    | None                    | Implemented in HCD Software.<br>Does not affect hardware.                                                                                                                 |

| GetHubStatus     | None                    | None                    | Implemented in HCD Software.<br>Does not affect hardware.                                                                                                                 |

| GetPortStatus    | Port Status And Control | 0, 1, 2, 3, 8,<br>9, 12 | Register Read. Reports Current<br>Connect Status and current<br>Connect Status Change; Port<br>Enable/Disable and<br>Enable/Disable Change; Low<br>Speed Device Attached. |

| SetHubDescriptor | None                    | None                    | Implemented in HCD Software.<br>Does not affect hardware.                                                                                                                 |

| SetHubFeature    | None                    | None                    | Not part of UHCI Design Guide                                                                                                                                             |

| SetPortFeature   | Port Status and Control | 0, 1, 2, 3, 8, 9,<br>12 | Register Write                                                                                                                                                            |

#### Table 1. Host Controller Register bit affected By Port Commands

#### 2. REGISTER DESCRIPTION

I/O registers are required for specific communications between the CPU and the Host Controller that are not efficiently handled via main system memory. The USB Host Controller module contains two sets of software accessible registers—I/O registers and optional PCI configuration registers. Note that the PCI configuration registers are only needed for PCI devices that implement the Host Controller.

- 1. **USB Host Controller I/O Registers.** This block of Control and Status registers is I/O mapped into PCI I/O space and controls the various operations of the USB (Table 2). The Base portion of the address location is set via a PCI configuration register.

- 2. PCI Configuration Registers (For PCI devices). In addition to the normal PCI header and device-specific registers, two registers are needed in the PCI Configuration space to support USB (Table 3). The normal PCI header and device specific registers are beyond the scope of this document (The CLASSC register is shown in this document). Note that HCD does not interact with the PCI configuration space. This space is used only by the PCI enumerator to identify the USB Host Controller, and assign the appropriate system resources.

The following notation is used to describe register access attributes:

- **RO Read Only.** If a register is read only, writes have no effect.

- WO Write Only. If a register is write only, reads have no effect.

- **R/W Read/Write**. A register with this attribute can be read and written. Note that individual bits in some read/write registers may be read only.

- **R/WC Read/Write Clear**. A register bit with this attribute can be read and written. However, a write of a 1 clears (sets to 0) the corresponding bit and a write of a 0 has no effect.

| I/O Address     | Mnemonic  | Register Description    | Register Access |

|-----------------|-----------|-------------------------|-----------------|

| Base + (00–01h) | USBCMD    | USB Command             | R/W             |

| Base + (02–03h) | USBSTS    | USB Status              | R/WC            |

| Base + (04–05h) | USBINTR   | USB Interrupt Enable    | R/W             |

| Base + (06–07h) | FRNUM     | Frame Number            | R/W**           |

| Base + (08–0Bh) | FRBASEADD | Frame List Base Address | R/W             |

| Base + 0Ch      | SOFMOD    | Start Of Frame Modify   | R/W             |

| Base + (10–11h) | PORTSC1   | Port 1 Status/Control   | R/WC**          |

| Base + (12–13h) | PORTSC2   | Port 2 Status/Control   | R/WC**          |

#### Table 2. USB Host/Controller I/O Registers

\*\* NOTE: These registers are WORD writeable only. Byte writes to these registers have unpredictable effects.

#### Table 3. PCI Configuration Registers For USB (PCI Devices Only)

| Configuration<br>Offset | Mnemonic | Register                                                  | Register<br>Access |

|-------------------------|----------|-----------------------------------------------------------|--------------------|

| 00–08h                  |          | Register implementation as needed for specific PCI device | —                  |

| 09–0Bh                  | CLASSC   | Class Code                                                | RO                 |

| 0C–1Fh                  | _        | Register implementation as needed for specific PCI device | _                  |

| 20–23h                  | USBBASE  | IO Space Base Address                                     | R/W                |

| 24–5Fh                  |          | Register implementation as needed for specific PCI device | _                  |

| 60h                     | SBRN     | Serial Bus Release Number                                 | RO                 |

| 61–FFh                  | _        | Register implementation as needed for specific PCI device | _                  |

#### 2.1 USB I/O Registers

This section describes the block of USB registers that are located in normal I/O space. The "base" portion of the I/O address is selected via a PCI Configuration register.

Some of the read/write register bits which deal with changing the state of the USB hub ports function such that on read back they reflect the current state of the port and not necessarily the state of the last write to the register. This allows the software to poll the state of the port and wait until it is in the proper state before proceeding. A Host Controller Reset, Global Reset, or Port Reset will immediately terminate a transfer on the affected ports and disable the port. This affects the USBCMD register, bit [4] and the PORTSC registers, bits [12,6,2]. See individual bit descriptions for more detail.

#### 2.1.1 USBCMD—USB COMMAND REGISTER

| Base+ (00–01h) |

|----------------|

| 0000h          |

| Read/Write     |

| 16 bits        |

|                |

The Command Register indicates the command to be executed by the serial bus host controller. Writing to the register causes a command to be executed. The table following the bit description provides additional information on the operation of the Run/Stop and Debug bits.

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7    | <b>Max Packet (MAXP).</b> 1=64 bytes. 0=32 bytes. This bit selects the maximum packet size that can be used for full speed bandwidth reclamation at the end of a frame. This value is used by the Host Controller to determine whether it should initiate another transaction based on the time remaining in the SOF counter. Use of reclamation packets larger than the programmed size will cause a Babble error if executed during the critical window at frame end. The Babble error results in the offending endpoint being stalled. Software is responsible for ensuring that any packet which could be executed under bandwidth reclamation be within this size limit. |

| 6    | <b>Configure Flag (CF).</b> HCD software sets this bit as the last action in its process of configuring the Host Controller. This bit has no effect on the hardware. It is provided only as a semaphore service for software.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | <b>Software Debug (SWDBG).</b> 1=Debug mode. 0=Normal Mode. In SW Debug mode, the Host Controller clears the Run/Stop bit after the completion of each USB transaction. The next transaction is executed when software sets the Run/Stop bit back to 1. The SWDBG bit must only be manipulated when the controller is in the stopped state. This can be determined by checking the HCHalted bit in the USBSTS register.                                                                                                                                                                                                                                                       |

| 4    | <b>Force Global Resume (FGR).</b> 1=Host Controller sends the Global Resume signal on the USB.<br>Software sets this bit to 0 after 20 ms has elapsed to stop sending the Global Resume signal. At that<br>time all USB devices should be ready for bus activity. The Host Controller sets this bit to 1 when a<br>resume event (connect, disconnect, or K-state) is detected while in global suspend mode. Software<br>resets this bit to 0 to end Global Resume signaling. The 1 to 0 transition causes the port to send a<br>low speed EOP signal. This bit will remain a 1 until the EOP has completed.                                                                   |

| 3    | <b>Enter Global Suspend Mode (EGSM).</b> 1=Host Controller enters the Global Suspend mode. No USB transactions occurs during this time. The Host Controller is able to receive resume signals from USB and interrupt the system. Software resets this bit to 0 to come out of Global Suspend mode. Software writes this bit to 0 at the same time that Force Global Resume (bit 4) is written to 0 or after writing bit 4 to 0. Software must also ensure that the Run/Stop bit (bit 0) is cleared prior to setting this bit.                                                                                                                                                 |

#### Universal Host Controller Interface (UHCI), Revision 1.1

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | <b>Global Reset (GRESET).</b> When this bit is set, the Host Controller sends the global reset signal on the USB and then resets all its logic, including the internal hub registers. The hub registers are reset to their power on state. This bit is reset by the software after a minimum of 10 ms has elapsed as specified in Chapter 7 of the USB Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | Note: Chip Hardware Reset has the same effect as Global Reset (bit 2), except that the Host Controller does not send the Global Reset on USB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1   | Host Controller Reset (HCRESET). When this bit is set, the Host Controller module resets its internal timers, counters, state machines, etc. to their initial value. Any transaction currently in progress on USB is immediately terminated. This bit is reset by the Host Controller when the reset process is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | The HCReset effects on Hub registers are slightly different from Chip Hardware Reset and Global USB Reset. The HCReset affects bits [8,3:0] of the Port Status and Control Register (PORTSC) of each port. HCReset resets the state machines of the Host Controller including the Connect/Disconnect state machine (one for each port). When the Connect/Disconnect state machine is reset, the output that signals connect/disconnect are negated to 0, effectively signaling a disconnect, even if a device is attached to the port. This virtual disconnect causes the port to be disabled. This disconnect and disabling of the port causes bit 1 (connect status change) and bit 3 (port enable/disable change) of the PORTSC to get set. The disconnect also causes bit 8 of PORTSC to reset. About 64 bit times after HCReset goes to 0, the connect and low-speed detect will take place and bits 0 and 8 of the PORTSC will change accordingly. |